FPGA用高速可逆データ圧縮IPコアシリーズ

画像データ・波形データなどの自然情報に特化した弊社オリジナルの可逆データ圧縮アルゴリズムCVC方式をFPGAで実現したIP Coreです。

これまでの圧縮

- 圧縮処理が重く時間がかかりすぎる

- データにより処理速度が大きく変動

- 回路規模が大きく、組み込みに不向き

- データの内容によっては圧縮率が低い

- フリーウェアではライセンスが不明瞭なことも

- 一般的な圧縮では解凍が容易にできてしまう

CVC Codecなら

- 従来方式に比べ、圧倒的な高速処理を実現

- データ入力後瞬時に圧縮開始、低レイテンシ設計

- 処理速度の変動が少なく、リアルタイム性に優れる

- コンパクトな回路規模で既存システムへの実装が容易

- 従来の可逆圧縮に比べ、高い圧縮率

- 独自処理のためセキュリティが高い

- ライセンスフリーの展開専用ライブラリ付き(機能制限版)

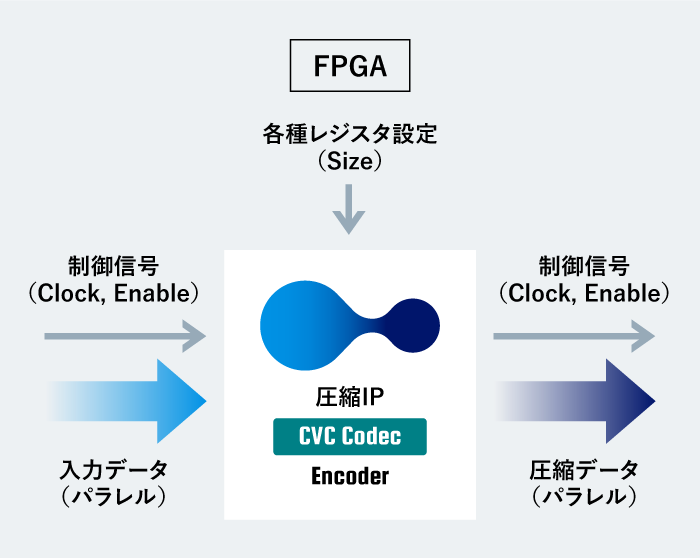

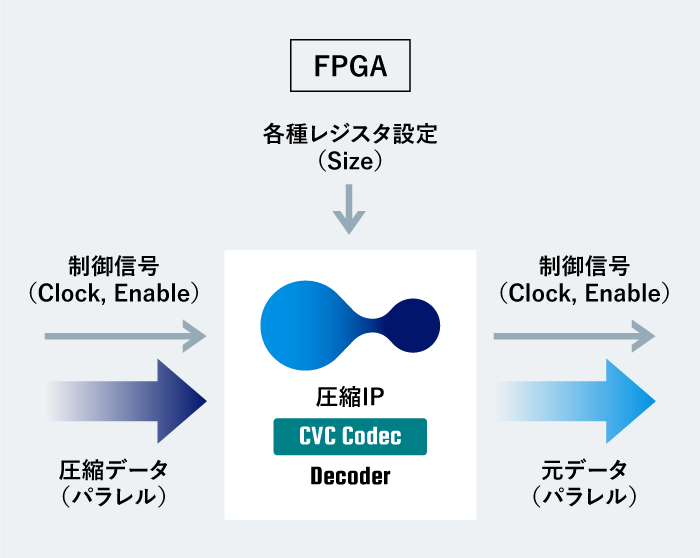

CVC Codecの利用イメージ

CVC Codecは、FIFOのようなイメージの構成になっており、入力データ(パラレル)と制御信号(Clock、Enableなど)のインターフェイスでデータを受け渡しします。

CVC Codec / Encoder

Encoderの入力データとして、センサーからのデジタルデータなどを入力することにより、2~10ラインのレイテンシで、圧縮データが出力されます。

CVC Codec / Decoder

Decoderの入力データとして、Encoderからの圧縮データなどを入力することにより、2~10ラインのレイテンシで、元データが出力されます。

ラインナップ

- 色空間(Gray/Bayer/RGB/YUV)

- 分解能(8~16bit)

- 処理速度(PixelClock x1/x2/x4/x8)

対応デバイス

- XILINX / ALTERA社 各種デバイス

詳細につきましては、お気軽にお問合せください。

CVC Codecの活用アイデア

外観検査装置(自動車/電子部品等)の画像データ全数保存

連続体(シート/パネル等)検査画像の全数保存

自動運転/先進安全システム用カメラデータの帯域確保・保存

IoT/クラウド/データセンター内の画像・波形データ圧縮

遠隔監視システムの通信高速化・省電力化

研究施設での実験データ保存